Menu

▾

▴

openocd-devel — Discuss development of OpenOCD

You can subscribe to this list here.

| 2001 |

Jan

|

Feb

|

Mar

|

Apr

|

May

|

Jun

|

Jul

|

Aug

|

Sep

(57) |

Oct

|

Nov

|

Dec

|

|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 2006 |

Jan

|

Feb

|

Mar

|

Apr

|

May

|

Jun

|

Jul

|

Aug

|

Sep

|

Oct

(14) |

Nov

(36) |

Dec

(7) |

| 2007 |

Jan

(48) |

Feb

(10) |

Mar

(17) |

Apr

(8) |

May

(35) |

Jun

(28) |

Jul

(50) |

Aug

(71) |

Sep

(40) |

Oct

(19) |

Nov

(22) |

Dec

(143) |

| 2008 |

Jan

(184) |

Feb

(549) |

Mar

(381) |

Apr

(388) |

May

(148) |

Jun

(128) |

Jul

(502) |

Aug

(243) |

Sep

(136) |

Oct

(327) |

Nov

(252) |

Dec

(475) |

| 2009 |

Jan

(344) |

Feb

(185) |

Mar

(338) |

Apr

(826) |

May

(1559) |

Jun

(1429) |

Jul

(817) |

Aug

(451) |

Sep

(639) |

Oct

(935) |

Nov

(1222) |

Dec

(826) |

| 2010 |

Jan

(552) |

Feb

(532) |

Mar

(355) |

Apr

(206) |

May

(162) |

Jun

(203) |

Jul

(168) |

Aug

(232) |

Sep

(270) |

Oct

(259) |

Nov

(439) |

Dec

(468) |

| 2011 |

Jan

(224) |

Feb

(249) |

Mar

(278) |

Apr

(381) |

May

(316) |

Jun

(637) |

Jul

(544) |

Aug

(465) |

Sep

(159) |

Oct

(440) |

Nov

(139) |

Dec

|

| 2012 |

Jan

(204) |

Feb

(383) |

Mar

(295) |

Apr

(196) |

May

(590) |

Jun

(158) |

Jul

(167) |

Aug

(177) |

Sep

(179) |

Oct

(301) |

Nov

(144) |

Dec

(173) |

| 2013 |

Jan

(299) |

Feb

(120) |

Mar

(238) |

Apr

(140) |

May

(69) |

Jun

(133) |

Jul

(160) |

Aug

(107) |

Sep

(164) |

Oct

(196) |

Nov

(105) |

Dec

(74) |

| 2014 |

Jan

(205) |

Feb

(156) |

Mar

(175) |

Apr

(181) |

May

(162) |

Jun

(158) |

Jul

(117) |

Aug

(109) |

Sep

(148) |

Oct

(106) |

Nov

(82) |

Dec

(72) |

| 2015 |

Jan

(191) |

Feb

(205) |

Mar

(197) |

Apr

(163) |

May

(136) |

Jun

(36) |

Jul

(79) |

Aug

(55) |

Sep

(64) |

Oct

(146) |

Nov

(142) |

Dec

(78) |

| 2016 |

Jan

(65) |

Feb

(190) |

Mar

(53) |

Apr

(38) |

May

(95) |

Jun

(53) |

Jul

(58) |

Aug

(113) |

Sep

(96) |

Oct

(59) |

Nov

(136) |

Dec

(124) |

| 2017 |

Jan

(80) |

Feb

(109) |

Mar

(163) |

Apr

(78) |

May

(61) |

Jun

(73) |

Jul

(29) |

Aug

(47) |

Sep

(60) |

Oct

(76) |

Nov

(48) |

Dec

(35) |

| 2018 |

Jan

(138) |

Feb

(84) |

Mar

(109) |

Apr

(49) |

May

(24) |

Jun

(62) |

Jul

(96) |

Aug

(116) |

Sep

(53) |

Oct

(99) |

Nov

(80) |

Dec

(88) |

| 2019 |

Jan

(100) |

Feb

(141) |

Mar

(72) |

Apr

(174) |

May

(129) |

Jun

(102) |

Jul

(52) |

Aug

(45) |

Sep

(28) |

Oct

(43) |

Nov

(78) |

Dec

(47) |

| 2020 |

Jan

(113) |

Feb

(72) |

Mar

(94) |

Apr

(141) |

May

(82) |

Jun

(68) |

Jul

(125) |

Aug

(76) |

Sep

(33) |

Oct

(184) |

Nov

(61) |

Dec

(95) |

| 2021 |

Jan

(109) |

Feb

(77) |

Mar

(145) |

Apr

(116) |

May

(134) |

Jun

(113) |

Jul

(71) |

Aug

(118) |

Sep

(116) |

Oct

(92) |

Nov

(124) |

Dec

(68) |

| 2022 |

Jan

(57) |

Feb

(61) |

Mar

(57) |

Apr

(74) |

May

(86) |

Jun

(80) |

Jul

(43) |

Aug

(85) |

Sep

(120) |

Oct

(88) |

Nov

(100) |

Dec

(108) |

| 2023 |

Jan

(39) |

Feb

(56) |

Mar

(92) |

Apr

(81) |

May

(84) |

Jun

(72) |

Jul

(182) |

Aug

(82) |

Sep

(54) |

Oct

(68) |

Nov

(67) |

Dec

(75) |

| 2024 |

Jan

(79) |

Feb

(65) |

Mar

(42) |

Apr

(47) |

May

(68) |

Jun

(111) |

Jul

(43) |

Aug

(73) |

Sep

(100) |

Oct

(35) |

Nov

(100) |

Dec

(99) |

| 2025 |

Jan

(71) |

Feb

(68) |

Mar

(44) |

Apr

(40) |

May

(92) |

Jun

(45) |

Jul

(86) |

Aug

|

Sep

|

Oct

|

Nov

|

Dec

|

|

From: <ge...@op...> - 2025-07-07 13:50:54

|

This is an automated email from Gerrit. "Ahmed Haoues <ahm...@st...>" just uploaded a new patch set to Gerrit, which you can find at https://review.openocd.org/c/openocd/+/8888 -- gerrit commit d5a65e9d983acd592c2ba7f9b4f6abd865bd72cf Author: HAOUES Ahmed <ahm...@st...> Date: Wed Jun 25 15:33:25 2025 +0100 flash/stm32h7x: Refactor STM32H7 flash register definitions to use enum Replace individual #define constants for STM32H7 flash registers with an enum to improve code readability and maintainability. Change-Id: Ib35cbdace5c2f4d12aa91c370d6ec0ce348b397f Signed-off-by: HAOUES Ahmed <ahm...@st...> diff --git a/src/flash/nor/stm32h7x.c b/src/flash/nor/stm32h7x.c index c02fae992c..6ecd265957 100644 --- a/src/flash/nor/stm32h7x.c +++ b/src/flash/nor/stm32h7x.c @@ -12,27 +12,47 @@ #include <target/algorithm.h> #include <target/cortex_m.h> - /* Erase time can be as high as 1000ms, 10x this and it's toast... */ #define FLASH_ERASE_TIMEOUT 10000 #define FLASH_WRITE_TIMEOUT 5 +#define MASS_ERASE_TIMEOUT 30000 + +enum stm32h7_flash_reg_index { + STM32_FLASH_ACR_INDEX, + STM32_FLASH_KEYR_INDEX, + STM32_FLASH_OPTKEYR_INDEX, + STM32_FLASH_SR_INDEX, + STM32_FLASH_CR_INDEX, + STM32_FLASH_ICR_INDEX, + STM32_FLASH_CCR_INDEX, + STM32_FLASH_OPTCR_INDEX, + STM32_FLASH_OPTSR_INDEX, + STM32_FLASH_OPTSR_CUR_INDEX, + STM32_FLASH_OPTSR_PRG_INDEX, + STM32_FLASH_OPTCCR_INDEX, + STM32_FLASH_WPSN_CUR_INDEX, + STM32_FLASH_WPSN_PRG_INDEX, + STM32_FLASH_ISR_INDEX, + STM32_FLASH_REG_INDEX_NUM, +}; /* RM 433 */ /* Same Flash registers for both banks, */ /* access depends on Flash Base address */ -#define FLASH_ACR 0x00 -#define FLASH_KEYR 0x04 -#define FLASH_OPTKEYR 0x08 -#define FLASH_CR 0x0C -#define FLASH_SR 0x10 -#define FLASH_CCR 0x14 -#define FLASH_OPTCR 0x18 -#define FLASH_OPTSR_CUR 0x1C -#define FLASH_OPTSR_PRG 0x20 -#define FLASH_OPTCCR 0x24 -#define FLASH_WPSN_CUR 0x38 -#define FLASH_WPSN_PRG 0x3C - +static const uint32_t stm32h7_flash_regs[STM32_FLASH_REG_INDEX_NUM] = { + [STM32_FLASH_ACR_INDEX] = 0x00, + [STM32_FLASH_KEYR_INDEX] = 0x04, + [STM32_FLASH_OPTKEYR_INDEX] = 0x08, + [STM32_FLASH_SR_INDEX] = 0x10, + [STM32_FLASH_CR_INDEX] = 0x0C, + [STM32_FLASH_CCR_INDEX] = 0x14, + [STM32_FLASH_OPTCR_INDEX] = 0x18, + [STM32_FLASH_OPTSR_CUR_INDEX] = 0x1C, + [STM32_FLASH_OPTSR_PRG_INDEX] = 0x20, + [STM32_FLASH_OPTCCR_INDEX] = 0x24, + [STM32_FLASH_WPSN_CUR_INDEX] = 0x38, + [STM32_FLASH_WPSN_PRG_INDEX] = 0x3C +}; /* FLASH_CR register bits */ #define FLASH_LOCK (1 << 0) @@ -117,6 +137,7 @@ struct stm32h7x_part_info { uint32_t wps_mask; /* function to compute flash_cr register values */ uint32_t (*compute_flash_cr)(uint32_t cmd, int snb); + int (*get_flash_error_status)(struct flash_bank *bank, uint32_t *status); }; struct stm32h7x_flash_bank { @@ -124,6 +145,7 @@ struct stm32h7x_flash_bank { uint32_t idcode; uint32_t user_bank_size; uint32_t flash_regs_base; /* Address of flash reg controller */ + const uint32_t *flash_regs; const struct stm32h7x_part_info *part_info; }; @@ -161,51 +183,56 @@ static uint32_t stm32h7a_h7bxx_compute_flash_cr(uint32_t cmd, int snb) return cmd | (tmp >> 2) | (snb << 6); } +static inline int stm32x_get_flash_status(struct flash_bank *bank, uint32_t *status); + static const struct stm32h7x_part_info stm32h7x_parts[] = { { - .id = DEVID_STM32H74_H75XX, - .revs = stm32h74_h75xx_revs, - .num_revs = ARRAY_SIZE(stm32h74_h75xx_revs), - .device_str = "STM32H74x/75x", - .page_size_kb = 128, - .block_size = 32, - .max_flash_size_kb = 2048, - .max_bank_size_kb = 1024, - .has_dual_bank = true, - .fsize_addr = 0x1FF1E880, - .wps_group_size = 1, - .wps_mask = 0xFF, - .compute_flash_cr = stm32h74_h75xx_compute_flash_cr, + .id = DEVID_STM32H74_H75XX, + .revs = stm32h74_h75xx_revs, + .num_revs = ARRAY_SIZE(stm32h74_h75xx_revs), + .device_str = "STM32H74x/75x", + .page_size_kb = 128, + .block_size = 32, + .max_flash_size_kb = 2048, + .max_bank_size_kb = 1024, + .has_dual_bank = true, + .fsize_addr = 0x1FF1E880, + .wps_group_size = 1, + .wps_mask = 0xFF, + .compute_flash_cr = stm32h74_h75xx_compute_flash_cr, + .get_flash_error_status = stm32x_get_flash_status, }, { - .id = DEVID_STM32H7A_H7BXX, - .revs = stm32h7a_h7bxx_revs, - .num_revs = ARRAY_SIZE(stm32h7a_h7bxx_revs), - .device_str = "STM32H7Ax/7Bx", - .page_size_kb = 8, - .block_size = 16, - .max_flash_size_kb = 2048, - .max_bank_size_kb = 1024, - .has_dual_bank = true, - .fsize_addr = 0x08FFF80C, - .wps_group_size = 4, - .wps_mask = 0xFFFFFFFF, - .compute_flash_cr = stm32h7a_h7bxx_compute_flash_cr, + .id = DEVID_STM32H7A_H7BXX, + .revs = stm32h7a_h7bxx_revs, + .num_revs = ARRAY_SIZE(stm32h7a_h7bxx_revs), + .device_str = "STM32H7Ax/7Bx", + .page_size_kb = 8, + .block_size = 16, + .max_flash_size_kb = 2048, + .max_bank_size_kb = 1024, + .has_dual_bank = true, + .fsize_addr = 0x08FFF80C, + .wps_group_size = 4, + .wps_mask = 0xFFFFFFFF, + .compute_flash_cr = stm32h7a_h7bxx_compute_flash_cr, + .get_flash_error_status = stm32x_get_flash_status, }, { - .id = DEVID_STM32H72_H73XX, - .revs = stm32h72_h73xx_revs, - .num_revs = ARRAY_SIZE(stm32h72_h73xx_revs), - .device_str = "STM32H72x/73x", - .page_size_kb = 128, - .block_size = 32, - .max_flash_size_kb = 1024, - .max_bank_size_kb = 1024, - .has_dual_bank = false, - .fsize_addr = 0x1FF1E880, - .wps_group_size = 1, - .wps_mask = 0xFF, - .compute_flash_cr = stm32h74_h75xx_compute_flash_cr, + .id = DEVID_STM32H72_H73XX, + .revs = stm32h72_h73xx_revs, + .num_revs = ARRAY_SIZE(stm32h72_h73xx_revs), + .device_str = "STM32H72x/73x", + .page_size_kb = 128, + .block_size = 32, + .max_flash_size_kb = 1024, + .max_bank_size_kb = 1024, + .has_dual_bank = false, + .fsize_addr = 0x1FF1E880, + .wps_group_size = 1, + .wps_mask = 0xFF, + .compute_flash_cr = stm32h74_h75xx_compute_flash_cr, + .get_flash_error_status = stm32x_get_flash_status, }, }; @@ -244,6 +271,13 @@ static inline int stm32x_read_flash_reg(struct flash_bank *bank, uint32_t reg_of return retval; } +static inline int stm32x_read_flash_reg_by_index(struct flash_bank *bank, + enum stm32h7_flash_reg_index reg_index, uint32_t *value) +{ + struct stm32h7x_flash_bank *stm32h7_info = bank->driver_priv; + return stm32x_read_flash_reg(bank, stm32h7_info->flash_regs[reg_index], value); +} + static inline int stm32x_write_flash_reg(struct flash_bank *bank, uint32_t reg_offset, uint32_t value) { uint32_t reg_addr = stm32x_get_flash_reg(bank, reg_offset); @@ -255,9 +289,16 @@ static inline int stm32x_write_flash_reg(struct flash_bank *bank, uint32_t reg_o return retval; } +static inline int stm32x_write_flash_reg_by_index(struct flash_bank *bank, + enum stm32h7_flash_reg_index reg_index, uint32_t value) +{ + struct stm32h7x_flash_bank *stm32h7_info = bank->driver_priv; + return stm32x_write_flash_reg(bank, stm32h7_info->flash_regs[reg_index], value); +} + static inline int stm32x_get_flash_status(struct flash_bank *bank, uint32_t *status) { - return stm32x_read_flash_reg(bank, FLASH_SR, status); + return stm32x_read_flash_reg_by_index(bank, STM32_FLASH_SR_INDEX, status); } static int stm32x_wait_flash_op_queue(struct flash_bank *bank, int timeout) @@ -291,7 +332,7 @@ static int stm32x_wait_flash_op_queue(struct flash_bank *bank, int timeout) if (retval == ERROR_OK) retval = ERROR_FAIL; /* If this operation fails, we ignore it and report the original retval */ - stm32x_write_flash_reg(bank, FLASH_CCR, status); + stm32x_write_flash_reg_by_index(bank, STM32_FLASH_CCR_INDEX, status); } return retval; } @@ -303,7 +344,7 @@ static int stm32x_unlock_reg(struct flash_bank *bank) /* first check if not already unlocked * otherwise writing on FLASH_KEYR will fail */ - int retval = stm32x_read_flash_reg(bank, FLASH_CR, &ctrl); + int retval = stm32x_read_flash_reg_by_index(bank, STM32_FLASH_CR_INDEX, &ctrl); if (retval != ERROR_OK) return retval; @@ -311,15 +352,15 @@ static int stm32x_unlock_reg(struct flash_bank *bank) return ERROR_OK; /* unlock flash registers for bank */ - retval = stm32x_write_flash_reg(bank, FLASH_KEYR, KEY1); + retval = stm32x_write_flash_reg_by_index(bank, STM32_FLASH_KEYR_INDEX, KEY1); if (retval != ERROR_OK) return retval; - retval = stm32x_write_flash_reg(bank, FLASH_KEYR, KEY2); + retval = stm32x_write_flash_reg_by_index(bank, STM32_FLASH_KEYR_INDEX, KEY2); if (retval != ERROR_OK) return retval; - retval = stm32x_read_flash_reg(bank, FLASH_CR, &ctrl); + retval = stm32x_read_flash_reg_by_index(bank, STM32_FLASH_CR_INDEX, &ctrl); if (retval != ERROR_OK) return retval; @@ -334,7 +375,7 @@ static int stm32x_unlock_option_reg(struct flash_bank *bank) { uint32_t ctrl; - int retval = stm32x_read_flash_reg(bank, FLASH_OPTCR, &ctrl); + int retval = stm32x_read_flash_reg_by_index(bank, STM32_FLASH_OPTCR_INDEX, &ctrl); if (retval != ERROR_OK) return retval; @@ -342,15 +383,15 @@ static int stm32x_unlock_option_reg(struct flash_bank *bank) return ERROR_OK; /* unlock option registers */ - retval = stm32x_write_flash_reg(bank, FLASH_OPTKEYR, OPTKEY1); + retval = stm32x_write_flash_reg_by_index(bank, STM32_FLASH_OPTKEYR_INDEX, OPTKEY1); if (retval != ERROR_OK) return retval; - retval = stm32x_write_flash_reg(bank, FLASH_OPTKEYR, OPTKEY2); + retval = stm32x_write_flash_reg_by_index(bank, STM32_FLASH_OPTKEYR_INDEX, OPTKEY2); if (retval != ERROR_OK) return retval; - retval = stm32x_read_flash_reg(bank, FLASH_OPTCR, &ctrl); + retval = stm32x_read_flash_reg_by_index(bank, STM32_FLASH_OPTCR_INDEX, &ctrl); if (retval != ERROR_OK) return retval; @@ -364,12 +405,12 @@ static int stm32x_unlock_option_reg(struct flash_bank *bank) static inline int stm32x_lock_reg(struct flash_bank *bank) { - return stm32x_write_flash_reg(bank, FLASH_CR, FLASH_LOCK); + return stm32x_write_flash_reg_by_index(bank, STM32_FLASH_CR_INDEX, FLASH_LOCK); } static inline int stm32x_lock_option_reg(struct flash_bank *bank) { - return stm32x_write_flash_reg(bank, FLASH_OPTCR, OPT_LOCK); + return stm32x_write_flash_reg_by_index(bank, STM32_FLASH_OPTCR_INDEX, OPT_LOCK); } static int stm32x_write_option(struct flash_bank *bank, uint32_t reg_offset, uint32_t value) @@ -382,17 +423,17 @@ static int stm32x_write_option(struct flash_bank *bank, uint32_t reg_offset, uin goto flash_options_lock; /* write option bytes */ - retval = stm32x_write_flash_reg(bank, reg_offset, value); + retval = stm32x_write_flash_reg_by_index(bank, reg_offset, value); if (retval != ERROR_OK) goto flash_options_lock; /* Remove OPT error flag before programming */ - retval = stm32x_write_flash_reg(bank, FLASH_OPTCCR, OPT_CLR_OPTCHANGEERR); + retval = stm32x_write_flash_reg_by_index(bank, STM32_FLASH_OPTCCR_INDEX, OPT_CLR_OPTCHANGEERR); if (retval != ERROR_OK) goto flash_options_lock; /* start programming cycle */ - retval = stm32x_write_flash_reg(bank, FLASH_OPTCR, OPT_START); + retval = stm32x_write_flash_reg_by_index(bank, STM32_FLASH_OPTCR_INDEX, OPT_START); if (retval != ERROR_OK) goto flash_options_lock; @@ -400,7 +441,7 @@ static int stm32x_write_option(struct flash_bank *bank, uint32_t reg_offset, uin int timeout = FLASH_ERASE_TIMEOUT; uint32_t status; for (;;) { - retval = stm32x_read_flash_reg(bank, FLASH_OPTSR_CUR, &status); + retval = stm32x_read_flash_reg_by_index(bank, STM32_FLASH_OPTSR_CUR_INDEX, &status); if (retval != ERROR_OK) { LOG_ERROR("stm32x_options_program: failed to read FLASH_OPTSR_CUR"); goto flash_options_lock; @@ -434,7 +475,7 @@ static int stm32x_modify_option(struct flash_bank *bank, uint32_t reg_offset, ui { uint32_t data; - int retval = stm32x_read_flash_reg(bank, reg_offset, &data); + int retval = stm32x_read_flash_reg_by_index(bank, reg_offset, &data); if (retval != ERROR_OK) return retval; @@ -448,7 +489,7 @@ static int stm32x_protect_check(struct flash_bank *bank) uint32_t protection; /* read 'write protection' settings */ - int retval = stm32x_read_flash_reg(bank, FLASH_WPSN_CUR, &protection); + int retval = stm32x_read_flash_reg_by_index(bank, STM32_FLASH_WPSN_CUR_INDEX, &protection); if (retval != ERROR_OK) { LOG_DEBUG("unable to read WPSN_CUR register"); return retval; @@ -488,13 +529,13 @@ static int stm32x_erase(struct flash_bank *bank, unsigned int first, */ for (unsigned int i = first; i <= last; i++) { LOG_DEBUG("erase sector %u", i); - retval = stm32x_write_flash_reg(bank, FLASH_CR, + retval = stm32x_write_flash_reg_by_index(bank, STM32_FLASH_CR_INDEX, stm32x_info->part_info->compute_flash_cr(FLASH_SER | FLASH_PSIZE_64, i)); if (retval != ERROR_OK) { LOG_ERROR("Error erase sector %u", i); goto flash_lock; } - retval = stm32x_write_flash_reg(bank, FLASH_CR, + retval = stm32x_write_flash_reg_by_index(bank, STM32_FLASH_CR_INDEX, stm32x_info->part_info->compute_flash_cr(FLASH_SER | FLASH_PSIZE_64 | FLASH_START, i)); if (retval != ERROR_OK) { LOG_ERROR("Error erase sector %u", i); @@ -529,7 +570,7 @@ static int stm32x_protect(struct flash_bank *bank, int set, unsigned int first, } /* read 'write protection' settings */ - int retval = stm32x_read_flash_reg(bank, FLASH_WPSN_CUR, &protection); + int retval = stm32x_read_flash_reg_by_index(bank, STM32_FLASH_WPSN_CUR_INDEX, &protection); if (retval != ERROR_OK) { LOG_DEBUG("unable to read WPSN_CUR register"); return retval; @@ -548,7 +589,7 @@ static int stm32x_protect(struct flash_bank *bank, int set, unsigned int first, LOG_DEBUG("stm32x_protect, option_bytes written WPSN 0x%" PRIx32, protection); /* apply new option value */ - return stm32x_write_option(bank, FLASH_WPSN_PRG, protection); + return stm32x_write_option(bank, STM32_FLASH_WPSN_PRG_INDEX, protection); } static int stm32x_write_block(struct flash_bank *bank, const uint8_t *buffer, @@ -641,7 +682,7 @@ static int stm32x_write_block(struct flash_bank *bank, const uint8_t *buffer, if ((flash_sr & FLASH_ERROR) != 0) { LOG_ERROR("flash write failed, FLASH_SR = 0x%08" PRIx32, flash_sr); /* Clear error + EOP flags but report errors */ - stm32x_write_flash_reg(bank, FLASH_CCR, flash_sr); + stm32x_write_flash_reg_by_index(bank, STM32_FLASH_CCR_INDEX, flash_sr); retval = ERROR_FAIL; } } @@ -711,7 +752,7 @@ static int stm32x_write(struct flash_bank *bank, const uint8_t *buffer, 4. Wait for flash operations completion */ while (blocks_remaining > 0) { - retval = stm32x_write_flash_reg(bank, FLASH_CR, + retval = stm32x_write_flash_reg_by_index(bank, STM32_FLASH_CR_INDEX, stm32x_info->part_info->compute_flash_cr(FLASH_PG | FLASH_PSIZE_64, 0)); if (retval != ERROR_OK) goto flash_lock; @@ -769,6 +810,8 @@ static int stm32x_probe(struct flash_bank *bank) device_id = stm32x_info->idcode & 0xfff; + stm32x_info->flash_regs = stm32h7_flash_regs; + for (unsigned int n = 0; n < ARRAY_SIZE(stm32h7x_parts); n++) { if (device_id == stm32h7x_parts[n].id) stm32x_info->part_info = &stm32h7x_parts[n]; @@ -967,7 +1010,7 @@ static int stm32x_set_rdp(struct flash_bank *bank, enum stm32h7x_opt_rdp new_rdp return ERROR_TARGET_NOT_HALTED; } - retval = stm32x_read_flash_reg(bank, FLASH_OPTSR_PRG, &optsr); + retval = stm32x_read_flash_reg_by_index(bank, STM32_FLASH_OPTSR_PRG_INDEX, &optsr); if (retval != ERROR_OK) { LOG_DEBUG("unable to read FLASH_OPTSR_PRG register"); @@ -997,7 +1040,7 @@ static int stm32x_set_rdp(struct flash_bank *bank, enum stm32h7x_opt_rdp new_rdp optsr = (optsr & ~OPT_RDP_MASK) | (new_rdp << OPT_RDP_POS); /* apply new option value */ - return stm32x_write_option(bank, FLASH_OPTSR_PRG, optsr); + return stm32x_write_option(bank, STM32_FLASH_OPTSR_PRG_INDEX, optsr); } COMMAND_HANDLER(stm32x_handle_lock_command) @@ -1056,17 +1099,17 @@ static int stm32x_mass_erase(struct flash_bank *bank) goto flash_lock; /* mass erase flash memory bank */ - retval = stm32x_write_flash_reg(bank, FLASH_CR, + retval = stm32x_write_flash_reg_by_index(bank, STM32_FLASH_CR_INDEX, stm32x_info->part_info->compute_flash_cr(FLASH_BER | FLASH_PSIZE_64, 0)); if (retval != ERROR_OK) goto flash_lock; - retval = stm32x_write_flash_reg(bank, FLASH_CR, + retval = stm32x_write_flash_reg_by_index(bank, STM32_FLASH_CR_INDEX, stm32x_info->part_info->compute_flash_cr(FLASH_BER | FLASH_PSIZE_64 | FLASH_START, 0)); if (retval != ERROR_OK) goto flash_lock; - retval = stm32x_wait_flash_op_queue(bank, 30000); + retval = stm32x_wait_flash_op_queue(bank, MASS_ERASE_TIMEOUT); if (retval != ERROR_OK) goto flash_lock; @@ -1110,7 +1153,7 @@ COMMAND_HANDLER(stm32x_handle_option_read_command) uint32_t reg_offset, value; COMMAND_PARSE_NUMBER(u32, CMD_ARGV[1], reg_offset); - retval = stm32x_read_flash_reg(bank, reg_offset, &value); + retval = stm32x_read_flash_reg_by_index(bank, reg_offset, &value); if (retval != ERROR_OK) return retval; -- |

|

From: <ge...@op...> - 2025-07-04 15:20:19

|

This is an automated email from Gerrit. "Antonio Borneo <bor...@gm...>" just uploaded a new patch set to Gerrit, which you can find at https://review.openocd.org/c/openocd/+/8984 -- gerrit commit 3b6fd1f8d8fe866d2e875d83d7fc5dab151465fc Author: Antonio Borneo <bor...@gm...> Date: Fri Jul 4 16:34:29 2025 +0200 tcl: stm32mp15x: modify handshake to open debug port, add hwthread Align the target script to the handshake implemented in the latest version of stm32wrapper4dbg to get access to the debug port. Use hwthread with the SMP node. Allow ignoring/masking some CPU from the configuration with the variables EN_<cpu>. Change-Id: I7117dd7df20b4f6b6e28f911e3e91ee763bdd200 Signed-off-by: Antonio Borneo <bor...@gm...> diff --git a/tcl/target/st/stm32mp15x.cfg b/tcl/target/st/stm32mp15x.cfg index bcdda73e90..9f52abaa6e 100644 --- a/tcl/target/st/stm32mp15x.cfg +++ b/tcl/target/st/stm32mp15x.cfg @@ -18,6 +18,11 @@ if { [info exists CHIPNAME] } { set _CHIPNAME stm32mp15x } +# Set to 0 to prevent CPU examine. Default examine them +if { ! [info exists EN_CA7_0] } { set EN_CA7_0 1 } +if { ! [info exists EN_CA7_1] } { set EN_CA7_1 1 } +if { ! [info exists EN_CM4] } { set EN_CM4 1 } + if { [info exists CPUTAPID] } { set _CPUTAPID $CPUTAPID } else { @@ -42,20 +47,21 @@ if { [using_jtag] } { dap create $_CHIPNAME.dap -chain-position $_CHIPNAME.tap -ignore-syspwrupack -# FIXME: Cortex-M code requires target accessible during reset, but this is not possible in STM32MP1 -# so defer-examine it until the reset framework get merged # NOTE: keep ap-num and dbgbase to speed-up examine after reset # NOTE: do not change the order of target create target create $_CHIPNAME.ap1 mem_ap -dap $_CHIPNAME.dap -ap-num 1 target create $_CHIPNAME.ap2 mem_ap -dap $_CHIPNAME.dap -ap-num 2 target create $_CHIPNAME.axi mem_ap -dap $_CHIPNAME.dap -ap-num 0 -target create $_CHIPNAME.cpu0 cortex_a -dap $_CHIPNAME.dap -ap-num 1 -coreid 0 -dbgbase 0xE00D0000 -target create $_CHIPNAME.cpu1 cortex_a -dap $_CHIPNAME.dap -ap-num 1 -coreid 1 -dbgbase 0xE00D2000 +target create $_CHIPNAME.cpu0 cortex_a -dap $_CHIPNAME.dap -ap-num 1 -coreid 0 -dbgbase 0xE00D0000 -defer-examine +target create $_CHIPNAME.cpu1 cortex_a -dap $_CHIPNAME.dap -ap-num 1 -coreid 1 -dbgbase 0xE00D2000 -defer-examine target create $_CHIPNAME.cm4 cortex_m -dap $_CHIPNAME.dap -ap-num 2 -defer-examine targets $_CHIPNAME.cpu0 target smp $_CHIPNAME.cpu0 $_CHIPNAME.cpu1 +$_CHIPNAME.cpu0 configure -rtos hwthread +$_CHIPNAME.cpu1 configure -rtos hwthread + $_CHIPNAME.cpu0 cortex_a maskisr on $_CHIPNAME.cpu1 cortex_a maskisr on $_CHIPNAME.cpu0 cortex_a dacrfixup on @@ -96,7 +102,16 @@ proc axi_nsecure {} { axi_secure -proc dbgmcu_enable_debug {} { +# mmw with target selection +proc target_mmw {target reg setbits clearbits} { + set val [eval $target read_memory $reg 32 1] + set val [expr {($val & ~$clearbits) | $setbits}] + eval $target mww $reg $val +} + +lappend _telnet_autocomplete_skip _enable_debug +# Uses AP1 +proc _enable_debug {} { # set debug enable bits in DBGMCU_CR to get ap2 and cm4 visible catch {$::_CHIPNAME.ap1 mww 0xe0081004 0x00000007} # freeze watchdog 1 and 2 on cores halted @@ -104,30 +119,70 @@ proc dbgmcu_enable_debug {} { catch {$::_CHIPNAME.ap1 mww 0xe008104c 0x00000008} } -proc toggle_cpu0_dbg_claim0 {} { - # toggle CPU0 DBG_CLAIM[0] - $::_CHIPNAME.ap1 mww 0xe00d0fa0 1 - $::_CHIPNAME.ap1 mww 0xe00d0fa4 1 +lappend _telnet_autocomplete_skip _handshake_with_wrapper +# Uses AP1 +proc _handshake_with_wrapper { halt } { + set dbgmcu_cr 0 + catch {set dbgmcu_cr [eval $::_CHIPNAME.ap1 read_memory 0xe0081004 32 1]} + if {[expr {($dbgmcu_cr & 0x07) == 0x00}]} { + echo "\nWARNING: FSBL wrapper not detected. Board in dev boot mode?\n" + return + } + + if { $halt } { + $::_CHIPNAME.ap1 arp_halt + if { $::EN_CA7_0 } { + $::_CHIPNAME.ap1 arp_halt + $::_CHIPNAME.ap1 mww 0xe00d0300 0 + target_mmw $::_CHIPNAME.ap1 0xe00d0088 0x00004000 0 + } + } + + $::_CHIPNAME.ap1 mww 0xe0081004 0x7 } -proc detect_cpu1 {} { +lappend _telnet_autocomplete_skip _detect_cpu1 +# Uses AP1 +proc _detect_cpu1 {} { + if { !$::EN_CA7_1 } { return } + set cpu1_prsr [$::_CHIPNAME.ap1 read_memory 0xE00D2314 32 1] set dual_core [expr {$cpu1_prsr & 1}] - if {! $dual_core} {$::_CHIPNAME.cpu1 configure -defer-examine} + if {!$dual_core} {set ::EN_CA7_1 0} } -proc rcc_enable_traceclk {} { +lappend _telnet_autocomplete_skip _rcc_enable_traceclk +proc _rcc_enable_traceclk {} { $::_CHIPNAME.ap2 mww 0x5000080c 0x301 } # FIXME: most of handler below will be removed once reset framework get merged -$_CHIPNAME.ap1 configure -event reset-deassert-pre {adapter deassert srst deassert trst;catch {dap init};catch {$::_CHIPNAME.dap apid 1}} -$_CHIPNAME.ap2 configure -event reset-deassert-pre {dbgmcu_enable_debug;rcc_enable_traceclk} -$_CHIPNAME.cpu0 configure -event reset-deassert-pre {$::_CHIPNAME.cpu0 arp_examine} -$_CHIPNAME.cpu1 configure -event reset-deassert-pre {$::_CHIPNAME.cpu1 arp_examine allow-defer} -$_CHIPNAME.cpu0 configure -event reset-deassert-post {toggle_cpu0_dbg_claim0} -$_CHIPNAME.cm4 configure -event reset-deassert-post {$::_CHIPNAME.cm4 arp_examine;if {[$::_CHIPNAME.ap2 curstate] == "halted"} {$::_CHIPNAME.cm4 arp_poll;$::_CHIPNAME.cm4 arp_poll;$::_CHIPNAME.cm4 arp_halt}} -$_CHIPNAME.ap1 configure -event examine-start {dap init} -$_CHIPNAME.ap2 configure -event examine-start {dbgmcu_enable_debug} -$_CHIPNAME.cpu0 configure -event examine-end {detect_cpu1} -$_CHIPNAME.ap2 configure -event examine-end {rcc_enable_traceclk;$::_CHIPNAME.cm4 arp_examine} +$_CHIPNAME.cm4 configure -event reset-assert { } + +$_CHIPNAME.ap1 configure -event reset-assert-post { adapter assert srst } + +$_CHIPNAME.ap1 configure -event reset-deassert-pre { + adapter deassert srst deassert trst + $::_CHIPNAME.ap1 arp_examine + _handshake_with_wrapper $halt + if { $::EN_CA7_0 } { $::_CHIPNAME.cpu0 arp_examine; if { $halt } { $::_CHIPNAME.cpu0 arp_halt }} + if { $::EN_CA7_1 } { $::_CHIPNAME.cpu1 arp_examine; if { $halt } { $::_CHIPNAME.cpu1 arp_halt }} + _enable_debug +} + +$_CHIPNAME.ap2 configure -event reset-deassert-pre { + _rcc_enable_traceclk + if { $::EN_CM4 } {$::_CHIPNAME.cm4 arp_examine; if { $halt } { $::_CHIPNAME.cm4 arp_halt }} +} + +$_CHIPNAME.ap1 configure -event examine-end { + _enable_debug + _detect_cpu1 + if { $::EN_CA7_0 } { $::_CHIPNAME.cpu0 arp_examine } + if { $::EN_CA7_1 } { $::_CHIPNAME.cpu1 arp_examine } +} + +$_CHIPNAME.ap2 configure -event examine-end { + _rcc_enable_traceclk + if { $::EN_CM4 } { $::_CHIPNAME.cm4 arp_examine } +} -- |

|

From: <ge...@op...> - 2025-07-04 15:20:18

|

This is an automated email from Gerrit. "Antonio Borneo <bor...@gm...>" just uploaded a new patch set to Gerrit, which you can find at https://review.openocd.org/c/openocd/+/8982 -- gerrit commit 35ba4ba066dd979b19f67a2a6e56fb4ab4811214 Author: Antonio Borneo <bor...@gm...> Date: Fri Jul 4 16:50:46 2025 +0200 tcl: move STM32 MPU files in vendor folder Move the existing files for STM32MP13x and STM32MP15x in the folder "st". Rename the boards using the correct separator "-" in place of "_". Change-Id: If8b92f55e3390ebc75df6a2ea09fcf798ea0b8cf Signed-off-by: Antonio Borneo <bor...@gm...> diff --git a/tcl/board/stm32mp13x_dk.cfg b/tcl/board/st/stm32mp13x-dk.cfg similarity index 83% rename from tcl/board/stm32mp13x_dk.cfg rename to tcl/board/st/stm32mp13x-dk.cfg index 8ece24844c..2259e0425b 100644 --- a/tcl/board/stm32mp13x_dk.cfg +++ b/tcl/board/st/stm32mp13x-dk.cfg @@ -7,6 +7,6 @@ source [find interface/stlink.cfg] transport select swd -source [find target/stm32mp13x.cfg] +source [find target/st/stm32mp13x.cfg] reset_config srst_only diff --git a/tcl/board/stm32mp15x_dk2.cfg b/tcl/board/st/stm32mp15x-dk2.cfg similarity index 87% rename from tcl/board/stm32mp15x_dk2.cfg rename to tcl/board/st/stm32mp15x-dk2.cfg index ba1c7f78a6..5d05307812 100644 --- a/tcl/board/stm32mp15x_dk2.cfg +++ b/tcl/board/st/stm32mp15x-dk2.cfg @@ -8,6 +8,6 @@ source [find interface/stlink.cfg] transport select swd -source [find target/stm32mp15x.cfg] +source [find target/st/stm32mp15x.cfg] reset_config srst_only diff --git a/tcl/file_renaming.cfg b/tcl/file_renaming.cfg index 0a3c7ba65b..b678f95582 100644 --- a/tcl/file_renaming.cfg +++ b/tcl/file_renaming.cfg @@ -17,6 +17,8 @@ set _file_renaming { board/nordic_nrf51822_mkit.cfg board/nordic/nrf51822-mkit.cfg board/nordic_nrf51_dk.cfg board/nordic/nrf51-dk.cfg board/nordic_nrf52_dk.cfg board/nordic/nrf52-dk.cfg + board/stm32mp13x_dk.cfg board/st/stm32mp13x-dk.cfg + board/stm32mp15x_dk2.cfg board/st/stm32mp15x-dk2.cfg target/nrf51.cfg target/nordic/nrf51.cfg target/nrf52.cfg target/nordic/nrf52.cfg target/nrf53.cfg target/nordic/nrf53.cfg diff --git a/tcl/target/stm32mp13x.cfg b/tcl/target/st/stm32mp13x.cfg similarity index 100% rename from tcl/target/stm32mp13x.cfg rename to tcl/target/st/stm32mp13x.cfg diff --git a/tcl/target/stm32mp15x.cfg b/tcl/target/st/stm32mp15x.cfg similarity index 100% rename from tcl/target/stm32mp15x.cfg rename to tcl/target/st/stm32mp15x.cfg -- |

|

From: <ge...@op...> - 2025-07-04 15:20:15

|

This is an automated email from Gerrit. "Antonio Borneo <bor...@gm...>" just uploaded a new patch set to Gerrit, which you can find at https://review.openocd.org/c/openocd/+/8983 -- gerrit commit 2021e38799291b7ce200519c9e6e41c77029e2b0 Author: Antonio Borneo <bor...@gm...> Date: Fri Jul 4 16:29:47 2025 +0200 tcl: stm32mp13x: modify handshake to open debug port Align the target script to the handshake implemented in the latest version of stm32wrapper4dbg to get access to the debug port. Change-Id: Ia1c7773330fda776abb4385331fddbf431d11c39 Signed-off-by: Antonio Borneo <bor...@gm...> diff --git a/tcl/target/st/stm32mp13x.cfg b/tcl/target/st/stm32mp13x.cfg index bcf25c9049..171b43fe97 100644 --- a/tcl/target/st/stm32mp13x.cfg +++ b/tcl/target/st/stm32mp13x.cfg @@ -46,7 +46,7 @@ dap create $_CHIPNAME.dap -chain-position $_CHIPNAME.tap -ignore-syspwrupack # NOTE: do not change the order of target create target create $_CHIPNAME.ap1 mem_ap -dap $_CHIPNAME.dap -ap-num 1 target create $_CHIPNAME.axi mem_ap -dap $_CHIPNAME.dap -ap-num 0 -target create $_CHIPNAME.cpu cortex_a -dap $_CHIPNAME.dap -ap-num 1 -coreid 0 -dbgbase 0xE00D0000 +target create $_CHIPNAME.cpu cortex_a -dap $_CHIPNAME.dap -ap-num 1 -coreid 0 -dbgbase 0xE00D0000 -defer-examine $_CHIPNAME.cpu cortex_a maskisr on $_CHIPNAME.cpu cortex_a dacrfixup on @@ -76,27 +76,55 @@ proc axi_nsecure {} { axi_secure -proc dbgmcu_enable_debug {} { +# mmw with target selection +proc target_mmw {target reg setbits clearbits} { + set val [eval $target read_memory $reg 32 1] + set val [expr {($val & ~$clearbits) | $setbits}] + eval $target mww $reg $val +} + +lappend _telnet_autocomplete_skip _enable_debug +# Uses AP1 +proc _enable_debug {} { # keep clock enabled in low-power - ## catch {$::_CHIPNAME.ap1 mww 0xe0081004 0x00000004} + catch {$::_CHIPNAME.ap1 mww 0xe0081004 0x00000004} # freeze watchdog 1 and 2 on core halted catch {$::_CHIPNAME.ap1 mww 0xe008102c 0x00000004} catch {$::_CHIPNAME.ap1 mww 0xe008104c 0x00000008} } -proc toggle_cpu_dbg_claim0 {} { - # toggle CPU0 DBG_CLAIM[0] - $::_CHIPNAME.ap1 mww 0xe00d0fa0 1 - $::_CHIPNAME.ap1 mww 0xe00d0fa4 1 +lappend _telnet_autocomplete_skip _handshake_with_wrapper +# Uses AP1 +proc _handshake_with_wrapper { halt } { + set dbgmcu_cr 0 + catch {set dbgmcu_cr [eval $::_CHIPNAME.ap1 read_memory 0xe0081004 32 1]} + if {[expr {($dbgmcu_cr & 0x07) == 0x00}]} { + echo "\nWARNING: FSBL wrapper not detected. Board in dev boot mode?\n" + return + } + + if { $halt } { + $::_CHIPNAME.ap1 arp_halt + $::_CHIPNAME.ap1 mww 0xe00d0300 0 + target_mmw $::_CHIPNAME.ap1 0xe00d0088 0x00004000 0 + } + + $::_CHIPNAME.ap1 mww 0xe0081004 0x7 } # FIXME: most of handlers below will be removed once reset framework get merged -$_CHIPNAME.ap1 configure -event reset-deassert-pre { +$_CHIPNAME.ap1 configure -event reset-assert-post { adapter assert srst } + +$_CHIPNAME.ap1 configure -event reset-deassert-pre { adapter deassert srst deassert trst - catch {dap init} - catch {$::_CHIPNAME.dap apid 1} + $::_CHIPNAME.ap1 arp_examine + _handshake_with_wrapper $halt + _enable_debug + $::_CHIPNAME.cpu arp_examine + if { $halt } { $::_CHIPNAME.cpu arp_halt} +} + +$_CHIPNAME.ap1 configure -event examine-end { + _enable_debug + $::_CHIPNAME.cpu arp_examine } -$_CHIPNAME.cpu configure -event reset-deassert-pre {$::_CHIPNAME.cpu arp_examine} -$_CHIPNAME.cpu configure -event reset-deassert-post {toggle_cpu_dbg_claim0; dbgmcu_enable_debug} -$_CHIPNAME.ap1 configure -event examine-start {dap init} -$_CHIPNAME.ap1 configure -event examine-end {dbgmcu_enable_debug} -- |

|

From: <ge...@op...> - 2025-07-04 15:20:15

|

This is an automated email from Gerrit. "Antonio Borneo <bor...@gm...>" just uploaded a new patch set to Gerrit, which you can find at https://review.openocd.org/c/openocd/+/8985 -- gerrit commit 12e7e1e2bf3e5a8d9b15336012fa7a95629a3284 Author: Antonio Borneo <bor...@gm...> Date: Fri Jul 4 16:37:38 2025 +0200 tcl: add support for stm32mp2xx targets and boards Add support for the targets stm32mp21x, stm32mp23x and stm32mp25x. Add support for the boards stm32mp23x-dk and stm32mp25x-dk. The board stm32mp21x-dk has no configuration file as it only provides a generic JTAG/SWD connector for the stm32mp21x SoC. Change-Id: I0256bebd8a5d5600066d8ae191d83344a35d3d37 Signed-off-by: Antonio Borneo <bor...@gm...> diff --git a/tcl/board/st/stm32mp23x-dk.cfg b/tcl/board/st/stm32mp23x-dk.cfg new file mode 100644 index 0000000000..1f660f19ed --- /dev/null +++ b/tcl/board/st/stm32mp23x-dk.cfg @@ -0,0 +1,12 @@ +# SPDX-License-Identifier: GPL-2.0-or-later + +# MB1605 with stm32mp23x +# https://www.st.com/en/evaluation-tools/stm32mp257f-dk.html + +source [find interface/stlink.cfg] + +transport select swd + +source [find target/st/stm32mp23x.cfg] + +reset_config srst_only diff --git a/tcl/board/st/stm32mp25x-dk.cfg b/tcl/board/st/stm32mp25x-dk.cfg new file mode 100644 index 0000000000..182f1d00ce --- /dev/null +++ b/tcl/board/st/stm32mp25x-dk.cfg @@ -0,0 +1,12 @@ +# SPDX-License-Identifier: GPL-2.0-or-later + +# MB1605 +# https://www.st.com/en/evaluation-tools/stm32mp257f-dk.html + +source [find interface/stlink.cfg] + +transport select swd + +source [find target/st/stm32mp25x.cfg] + +reset_config srst_only diff --git a/tcl/target/st/stm32mp21x.cfg b/tcl/target/st/stm32mp21x.cfg new file mode 100644 index 0000000000..22532031ff --- /dev/null +++ b/tcl/target/st/stm32mp21x.cfg @@ -0,0 +1,199 @@ +# SPDX-License-Identifier: GPL-2.0-or-later + +# STMicroelectronics STM32MP21x +# STM32MP21x devices support both JTAG and SWD transports. + +# HLA does not support multi-cores nor custom CSW nor AP other than 0 +if { [using_hla] } { + echo "ERROR: HLA transport cannot work with this target." + shutdown +} + +source [find target/swj-dp.tcl] +source [find mem_helper.tcl] + +if { [info exists CHIPNAME] } { + set _CHIPNAME $CHIPNAME +} else { + set _CHIPNAME stm32mp21x +} + +# Set to 0 to prevent CPU examine. Default examine them +if { ! [info exists EN_CA35] } { set EN_CA35 1 } +if { ! [info exists EN_CM33] } { set EN_CM33 1 } + +set _ENDIAN little + +# jtag scan chain +if { [info exists CPUTAPID] } { + set _CPUTAPID $CPUTAPID +} else { + if { [using_jtag] } { + set _CPUTAPID 0x6ba00477 + } { + set _CPUTAPID 0x6ba02477 + } +} + +# Chip Level TAP Controller, only in jtag mode +if { [info exists CLCTAPID] } { + set _CLCTAPID $CLCTAPID +} else { + set _CLCTAPID 0x16503041 +} + +swj_newdap $_CHIPNAME tap -expected-id $_CPUTAPID -irlen 4 -ircapture 0x01 -irmask 0x0f +if { [using_jtag] } { + swj_newdap $_CHIPNAME.clc tap -expected-id $_CLCTAPID -irlen 5 +} + +dap create $_CHIPNAME.dap -chain-position $_CHIPNAME.tap + +# define AXI & APB Memory Access Ports +# NOTE: do not change the order of target create +target create $_CHIPNAME.ap0 mem_ap -dap $_CHIPNAME.dap -ap-num 0 +target create $_CHIPNAME.ap1 mem_ap -dap $_CHIPNAME.dap -ap-num 1 +target create $_CHIPNAME.axi mem_ap -dap $_CHIPNAME.dap -ap-num 2 +target create $_CHIPNAME.ap3 mem_ap -dap $_CHIPNAME.dap -ap-num 3 -defer-examine + +# define the Cortex-A35 +cti create $_CHIPNAME.cti.a35 -dap $_CHIPNAME.dap -ap-num 1 -baseaddr 0x80220000 +target create $_CHIPNAME.a35 aarch64 -dap $_CHIPNAME.dap -ap-num 1 -dbgbase 0x80210000 \ + -cti $_CHIPNAME.cti.a35 -defer-examine + +# define the Cortex-M33 +target create $_CHIPNAME.m33 cortex_m -dap $_CHIPNAME.dap -ap-num 3 -defer-examine +cti create $_CHIPNAME.cti.m33 -dap $_CHIPNAME.dap -ap-num 3 -baseaddr 0xe0042000 + +# define the system CTIs +cti create $_CHIPNAME.cti.sys0 -dap $_CHIPNAME.dap -ap-num 1 -baseaddr 0x80080000 +cti create $_CHIPNAME.cti.sys1 -dap $_CHIPNAME.dap -ap-num 1 -baseaddr 0x80090000 + +swo create $_CHIPNAME.swo -dap $_CHIPNAME.dap -ap-num 1 -baseaddr 0x800A0000 +tpiu create $_CHIPNAME.tpiu -dap $_CHIPNAME.dap -ap-num 1 -baseaddr 0x80040000 + +targets $_CHIPNAME.a35 + +reset_config srst_pulls_trst + +adapter speed 5000 +adapter srst pulse_width 200 +# wait 1 seconds for bootrom +adapter srst delay 1000 + +# set CSW for AXI +$_CHIPNAME.dap apsel 2 +$_CHIPNAME.dap apcsw 0x12800000 + +# mmw with target selection +proc target_mmw {target reg setbits clearbits} { + set val [eval $target read_memory $reg 32 1] + set val [expr {($val & ~$clearbits) | $setbits}] + eval $target mww $reg $val +} + +lappend _telnet_autocomplete_skip _enable_debug +# Uses AP0 and AXI +proc _enable_debug {} { + # Enable DBGMCU clock in RC + $::_CHIPNAME.axi mww 0x44200520 0x500 + + # set debug enable bits in DBGMCU_CR to get ap3/cm33 visible + $::_CHIPNAME.ap0 mww 0x80001004 0x7 + + # Freeze watchdogs on CPU halt + $::_CHIPNAME.axi mww 0x440a003c 0x00000026 + $::_CHIPNAME.axi mww 0x440a0040 0x00000038 +} + +lappend _telnet_autocomplete_skip _rcc_enable_traceclk +# Uses AXI +proc _rcc_enable_traceclk {} { + # set bit TRACEEN in RCC_DBGCFGR to clock TPIU + target_mmw $::_CHIPNAME.axi 0x44200520 0x200 0 +} + +lappend _telnet_autocomplete_skip _handshake_with_wrapper +# Uses AP0, AP1 and AP3 +proc _handshake_with_wrapper { halt } { + set dbgmcu_cr 0 + catch {set dbgmcu_cr [eval $::_CHIPNAME.ap0 read_memory 0x80001004 32 1]} + if {[expr {($dbgmcu_cr & 0x07) == 0x00}]} { + echo "\nWARNING: FSBL wrapper not detected. Board in dev boot mode?\n" + return + } + + if { $halt } { + if { $::EN_CA35 } { + $::_CHIPNAME.ap1 arp_examine + $::_CHIPNAME.ap1 arp_halt + $::_CHIPNAME.ap1 mww 0x80210300 0 + target_mmw $::_CHIPNAME.ap1 0x80210088 0x00004000 0 + } + if { $::EN_CM33 } { + $::_CHIPNAME.ap3 arp_examine + $::_CHIPNAME.ap3 arp_halt + $::_CHIPNAME.ap3 mww 0xe000edf0 0xa05f0001 + } + } + + # alert wrapper that debugger is ready + $::_CHIPNAME.ap0 mww 0x80001004 0x07 +} + +lappend _telnet_autocomplete_skip _enable_dbgmcu_on_devboot +# In DEV BOOT the BootROM does not completes the sequence to enable the +# visibility of DBGMCU on AP0. +# Write a value in DBGMCU_DBG_AUTH_DEV from CID1. +# Returns 1 if DEV BOOT is detected +# Uses AP2 (AXI bus) +proc _enable_dbgmcu_on_devboot {} { + $::_CHIPNAME.axi mww 0x44230004 0 + set boot_pins [expr {[$::_CHIPNAME.axi read_memory 0x44230000 32 1] & 0xf}] + if {$boot_pins != 0x3 && $boot_pins != 0xc} { + return 0 + } + + set rifsc_rimc_cr [$::_CHIPNAME.axi read_memory 0x42080c00 32 1] + if {$rifsc_rimc_cr != 0x00008710} { + echo "RIFSC_RIMC_CR modified, skip activation of DBGMCU" + return 1 + } + + # Enable DBGMCU clock in RC + $::_CHIPNAME.axi mww 0x44200520 0x500 + + # Change DAP (AXI) CID, write in DBGMCU, set back DAP CID + $::_CHIPNAME.axi mww 0x42080c00 0x00008110 + $::_CHIPNAME.axi mww 0x440A0104 1 + $::_CHIPNAME.axi mww 0x42080c00 0x00008710 + return 1 +} + +$_CHIPNAME.m33 configure -event reset-assert { } + +$_CHIPNAME.axi configure -event reset-assert-post { adapter assert srst } + +$_CHIPNAME.axi configure -event reset-deassert-pre { + adapter deassert srst deassert trst + $::_CHIPNAME.axi arp_examine + set is_dev_boot [_enable_dbgmcu_on_devboot] + if { !$is_dev_boot } { _handshake_with_wrapper $halt} + _enable_debug + _rcc_enable_traceclk + if { $::EN_CA35 } { $::_CHIPNAME.a35 arp_examine; if {$halt} {$::_CHIPNAME.a35 arp_halt} } + if { $::EN_CM33 } { + $::_CHIPNAME.ap3 arp_examine + $::_CHIPNAME.m33 arp_examine + if {$halt} {$::_CHIPNAME.ap3 arp_halt; $::_CHIPNAME.m33 arp_halt} + } +} + +$_CHIPNAME.axi configure -event examine-end { + set is_dev_boot [_enable_dbgmcu_on_devboot] + if {$is_dev_boot} {echo "Dev boot detected"} + _enable_debug + _rcc_enable_traceclk + if { $::EN_CA35 } { $::_CHIPNAME.a35 arp_examine } + if { $::EN_CM33 } { $::_CHIPNAME.ap3 arp_examine; $::_CHIPNAME.m33 arp_examine } +} diff --git a/tcl/target/st/stm32mp23x.cfg b/tcl/target/st/stm32mp23x.cfg new file mode 100644 index 0000000000..ad148608bc --- /dev/null +++ b/tcl/target/st/stm32mp23x.cfg @@ -0,0 +1,188 @@ +# SPDX-License-Identifier: GPL-2.0-or-later + +# STMicroelectronics STM32MP23x +# STM32MP23x devices support both JTAG and SWD transports. + +# HLA does not support multi-cores nor custom CSW nor AP other than 0 +if { [using_hla] } { + echo "ERROR: HLA transport cannot work with this target." + shutdown +} + +source [find target/swj-dp.tcl] +source [find mem_helper.tcl] + +if { [info exists CHIPNAME] } { + set _CHIPNAME $CHIPNAME +} else { + set _CHIPNAME stm32mp23x +} + +# Set to 0 to prevent CPU examine. Default examine them +if { ! [info exists EN_CA35_0] } { set EN_CA35_0 1 } +if { ! [info exists EN_CA35_1] } { set EN_CA35_1 1 } +if { ! [info exists EN_CM33] } { set EN_CM33 1 } + +set _ENDIAN little + +# jtag scan chain +if { [info exists CPUTAPID] } { + set _CPUTAPID $CPUTAPID +} else { + if { [using_jtag] } { + set _CPUTAPID 0x6ba00477 + } { + set _CPUTAPID 0x6ba02477 + } +} + +# Chip Level TAP Controller, only in jtag mode +if { [info exists CLCTAPID] } { + set _CLCTAPID $CLCTAPID +} else { + set _CLCTAPID 0x16505041 +} + +swj_newdap $_CHIPNAME tap -expected-id $_CPUTAPID -irlen 4 -ircapture 0x01 -irmask 0x0f +if { [using_jtag] } { + swj_newdap $_CHIPNAME.clc tap -expected-id $_CLCTAPID -irlen 5 +} + +dap create $_CHIPNAME.dap -chain-position $_CHIPNAME.tap + +# define AXI & APB Memory Access Ports +# NOTE: do not change the order of target create +target create $_CHIPNAME.ap0 mem_ap -dap $_CHIPNAME.dap -ap-num 0 +target create $_CHIPNAME.axi mem_ap -dap $_CHIPNAME.dap -ap-num 4 +target create $_CHIPNAME.ap8 mem_ap -dap $_CHIPNAME.dap -ap-num 8 -defer-examine + +# define the first Cortex-A35 +cti create $_CHIPNAME.cti.a35_0 -dap $_CHIPNAME.dap -ap-num 0 -baseaddr 0x80220000 +target create $_CHIPNAME.a35_0 aarch64 -dap $_CHIPNAME.dap -ap-num 0 -dbgbase 0x80210000 \ + -cti $_CHIPNAME.cti.a35_0 -defer-examine + +# define the second Cortex-A35 +cti create $_CHIPNAME.cti.a35_1 -dap $_CHIPNAME.dap -ap-num 0 -baseaddr 0x80320000 +target create $_CHIPNAME.a35_1 aarch64 -dap $_CHIPNAME.dap -ap-num 0 -dbgbase 0x80310000 \ + -cti $_CHIPNAME.cti.a35_1 -defer-examine + +# define the Cortex-M33 +target create $_CHIPNAME.m33 cortex_m -dap $_CHIPNAME.dap -ap-num 8 -defer-examine +cti create $_CHIPNAME.cti.m33 -dap $_CHIPNAME.dap -ap-num 8 -baseaddr 0xe0042000 + +# define the system CTIs +cti create $_CHIPNAME.cti.sys0 -dap $_CHIPNAME.dap -ap-num 0 -baseaddr 0x80090000 +cti create $_CHIPNAME.cti.sys1 -dap $_CHIPNAME.dap -ap-num 0 -baseaddr 0x800a0000 + +swo create $_CHIPNAME.swo -dap $_CHIPNAME.dap -ap-num 0 -baseaddr 0x800b0000 +tpiu create $_CHIPNAME.tpiu -dap $_CHIPNAME.dap -ap-num 0 -baseaddr 0x80050000 + +targets $_CHIPNAME.a35_0 + +target smp $_CHIPNAME.a35_0 $_CHIPNAME.a35_1 +$_CHIPNAME.a35_0 configure -rtos hwthread +$_CHIPNAME.a35_1 configure -rtos hwthread + +reset_config srst_gates_jtag srst_pulls_trst + +adapter speed 5000 +adapter srst pulse_width 200 +# wait 1 seconds for bootrom +adapter srst delay 1000 + +# set CSW for AXI +$_CHIPNAME.dap apsel 4 +$_CHIPNAME.dap apcsw 0x12800000 + +# mmw with target selection +proc target_mmw {target reg setbits clearbits} { + set val [eval $target read_memory $reg 32 1] + set val [expr {($val & ~$clearbits) | $setbits}] + eval $target mww $reg $val +} + +lappend _telnet_autocomplete_skip _enable_debug +# Uses AP0 and AXI +proc _enable_debug {} { + # set debug enable bits in DBGMCU_CR to get ap8/cm33 visible + $::_CHIPNAME.ap0 mww 0x80010004 0x17 + + # Freeze watchdogs on CPU halt + $::_CHIPNAME.axi mww 0x4a010008 0x00000000 + $::_CHIPNAME.axi mww 0x4a01003c 0x00000026 + $::_CHIPNAME.axi mww 0x4a010040 0x00000038 + $::_CHIPNAME.axi mww 0x4a010044 0x00000400 + $::_CHIPNAME.axi mww 0x4a010048 0x00000400 + $::_CHIPNAME.axi mww 0x4a01004c 0x00000600 +} + +lappend _telnet_autocomplete_skip _rcc_enable_traceclk +# Uses AXI +proc _rcc_enable_traceclk {} { + # set bit TRACEEN in RCC_DBGCFGR to clock TPIU + target_mmw $::_CHIPNAME.axi 0x44200520 0x200 0 +} + +lappend _telnet_autocomplete_skip _handshake_with_wrapper +# Uses AP0 +proc _handshake_with_wrapper { halt } { + set dbgmcu_cr 0 + catch {set dbgmcu_cr [eval $::_CHIPNAME.ap0 read_memory 0x80010004 32 1]} + if {[expr {($dbgmcu_cr & 0x07) == 0x00}]} { + echo "\nWARNING: FSBL wrapper not detected. Board in dev boot mode?\n" + return; + } + + if { $halt } { + if { $::EN_CA35_0 || $::EN_CA35_1 } { + $::_CHIPNAME.ap0 arp_examine + $::_CHIPNAME.ap0 arp_halt + } + if { $::EN_CA35_0 } { + $::_CHIPNAME.ap0 mww 0x80210300 0 + target_mmw $::_CHIPNAME.ap0 0x80210088 0x00004000 0 + } + if { $::EN_CA35_1 } { + $::_CHIPNAME.ap0 mww 0x80310300 0 + target_mmw $::_CHIPNAME.ap0 0x80310088 0x00004000 0 + } + if { $::EN_CM33 } { + $::_CHIPNAME.ap8 arp_examine + $::_CHIPNAME.ap8 arp_halt + $::_CHIPNAME.ap8 mww 0xe000edf0 0xa05f0001 + } + } + + # alert wrapper that debugger is ready + $::_CHIPNAME.ap0 mww 0x80010004 0x17 +} + +$_CHIPNAME.m33 configure -event reset-assert { } + +$_CHIPNAME.axi configure -event reset-assert-post { adapter assert srst } + +$_CHIPNAME.axi configure -event reset-deassert-pre { + adapter deassert srst deassert trst + + $::_CHIPNAME.ap0 arp_examine + _handshake_with_wrapper $halt + + $::_CHIPNAME.axi arp_examine + _enable_debug + _rcc_enable_traceclk + if { $::EN_CA35_0 } { $::_CHIPNAME.a35_0 arp_examine; if {$halt} {$::_CHIPNAME.a35_0 arp_halt} } + if { $::EN_CA35_1 } { $::_CHIPNAME.a35_1 arp_examine; if {$halt} {$::_CHIPNAME.a35_1 arp_halt} } + if { $::EN_CM33 } { + $::_CHIPNAME.ap8 arp_examine + $::_CHIPNAME.m33 arp_examine + if {$halt} {$::_CHIPNAME.m33 arp_halt} + } +} + +$_CHIPNAME.axi configure -event examine-end { + _enable_debug + _rcc_enable_traceclk + if { $::EN_CA35_0 } { $::_CHIPNAME.a35_0 arp_examine } + if { $::EN_CA35_1 } { $::_CHIPNAME.a35_1 arp_examine } + if { $::EN_CM33 } { $::_CHIPNAME.ap8 arp_examine; $::_CHIPNAME.m33 arp_examine } +} diff --git a/tcl/target/st/stm32mp25x.cfg b/tcl/target/st/stm32mp25x.cfg new file mode 100644 index 0000000000..97802903fb --- /dev/null +++ b/tcl/target/st/stm32mp25x.cfg @@ -0,0 +1,210 @@ +# SPDX-License-Identifier: GPL-2.0-or-later + +# STMicroelectronics STM32MP25x +# STM32MP25x devices support both JTAG and SWD transports. + +# HLA does not support multi-cores nor custom CSW nor AP other than 0 +if { [using_hla] } { + echo "ERROR: HLA transport cannot work with this target." + shutdown +} + +source [find target/swj-dp.tcl] +source [find mem_helper.tcl] + +if { [info exists CHIPNAME] } { + set _CHIPNAME $CHIPNAME +} else { + set _CHIPNAME stm32mp25x +} + +# Set to 0 to prevent CPU examine. Default examine them +if { ! [info exists EN_CA35_0] } { set EN_CA35_0 1 } +if { ! [info exists EN_CA35_1] } { set EN_CA35_1 1 } +if { ! [info exists EN_CM33] } { set EN_CM33 1 } +if { ! [info exists EN_CM0P] } { set EN_CM0P 1 } + +set _ENDIAN little + +# jtag scan chain +if { [info exists CPUTAPID] } { + set _CPUTAPID $CPUTAPID +} else { + if { [using_jtag] } { + set _CPUTAPID 0x6ba00477 + } { + set _CPUTAPID 0x6ba02477 + } +} + +# Chip Level TAP Controller, only in jtag mode +if { [info exists CLCTAPID] } { + set _CLCTAPID $CLCTAPID +} else { + set _CLCTAPID 0x16505041 +} + +swj_newdap $_CHIPNAME tap -expected-id $_CPUTAPID -irlen 4 -ircapture 0x01 -irmask 0x0f +if { [using_jtag] } { + swj_newdap $_CHIPNAME.clc tap -expected-id $_CLCTAPID -irlen 5 +} + +dap create $_CHIPNAME.dap -chain-position $_CHIPNAME.tap + +# define AXI & APB Memory Access Ports +# NOTE: do not change the order of target create +target create $_CHIPNAME.ap0 mem_ap -dap $_CHIPNAME.dap -ap-num 0 +target create $_CHIPNAME.axi mem_ap -dap $_CHIPNAME.dap -ap-num 4 +target create $_CHIPNAME.ap2 mem_ap -dap $_CHIPNAME.dap -ap-num 2 -defer-examine +target create $_CHIPNAME.ap8 mem_ap -dap $_CHIPNAME.dap -ap-num 8 -defer-examine + +# define the first Cortex-A35 +cti create $_CHIPNAME.cti.a35_0 -dap $_CHIPNAME.dap -ap-num 0 -baseaddr 0x80220000 +target create $_CHIPNAME.a35_0 aarch64 -dap $_CHIPNAME.dap -ap-num 0 -dbgbase 0x80210000 \ + -cti $_CHIPNAME.cti.a35_0 -defer-examine + +# define the second Cortex-A35 +cti create $_CHIPNAME.cti.a35_1 -dap $_CHIPNAME.dap -ap-num 0 -baseaddr 0x80320000 +target create $_CHIPNAME.a35_1 aarch64 -dap $_CHIPNAME.dap -ap-num 0 -dbgbase 0x80310000 \ + -cti $_CHIPNAME.cti.a35_1 -defer-examine + +# define the Cortex-M33 +target create $_CHIPNAME.m33 cortex_m -dap $_CHIPNAME.dap -ap-num 8 -defer-examine +cti create $_CHIPNAME.cti.m33 -dap $_CHIPNAME.dap -ap-num 8 -baseaddr 0xe0042000 + +# define the Cortex-M0+ +target create $_CHIPNAME.m0p cortex_m -dap $_CHIPNAME.dap -ap-num 2 -defer-examine +cti create $_CHIPNAME.cti.m0p -dap $_CHIPNAME.dap -ap-num 2 -baseaddr 0xf0000000 + +# define the system CTIs +cti create $_CHIPNAME.cti.sys0 -dap $_CHIPNAME.dap -ap-num 0 -baseaddr 0x80090000 +cti create $_CHIPNAME.cti.sys1 -dap $_CHIPNAME.dap -ap-num 0 -baseaddr 0x800a0000 + +swo create $_CHIPNAME.swo -dap $_CHIPNAME.dap -ap-num 0 -baseaddr 0x800b0000 +tpiu create $_CHIPNAME.tpiu -dap $_CHIPNAME.dap -ap-num 0 -baseaddr 0x80050000 + +targets $_CHIPNAME.a35_0 + +target smp $_CHIPNAME.a35_0 $_CHIPNAME.a35_1 +$_CHIPNAME.a35_0 configure -rtos hwthread +$_CHIPNAME.a35_1 configure -rtos hwthread + +reset_config srst_gates_jtag srst_pulls_trst + +adapter speed 5000 +adapter srst pulse_width 200 +# wait 1 seconds for bootrom +adapter srst delay 1000 + +# set CSW for AXI +$_CHIPNAME.dap apsel 4 +$_CHIPNAME.dap apcsw 0x12800000 + +# mmw with target selection +proc target_mmw {target reg setbits clearbits} { + set val [eval $target read_memory $reg 32 1] + set val [expr {($val & ~$clearbits) | $setbits}] + eval $target mww $reg $val +} + +lappend _telnet_autocomplete_skip _enable_ap2_cm0p +proc _enable_ap2_cm0p {} { + # set bits C3LPEN and C3EN in RCC_C3CFGR to enable AP2 and CM0+ clock + target_mmw $::_CHIPNAME.axi 0x54200490 6 0 +} + +lappend _telnet_autocomplete_skip _enable_debug +# Uses AP0 and AXI +proc _enable_debug {} { + # set debug enable bits in DBGMCU_CR to get ap2/cm0+ and ap8/cm33 visible + # set DBG_SWD_SEL_N bit in DBGMCU_CR to get ap2/cm0+ on main debug interface + $::_CHIPNAME.ap0 mww 0x80010004 0x17 + + if { $::EN_CM0P } { + _enable_ap2_cm0p + } + + # Freeze watchdogs on CPU halt + $::_CHIPNAME.axi mww 0x4a010008 0x00000000 + $::_CHIPNAME.axi mww 0x4a01003c 0x00000026 + $::_CHIPNAME.axi mww 0x4a010040 0x00000038 + $::_CHIPNAME.axi mww 0x4a010044 0x00000400 + $::_CHIPNAME.axi mww 0x4a010048 0x00000400 + $::_CHIPNAME.axi mww 0x4a01004c 0x00000600 +} + +lappend _telnet_autocomplete_skip _rcc_enable_traceclk +# Uses AXI +proc _rcc_enable_traceclk {} { + # set bit TRACEEN in RCC_DBGCFGR to clock TPIU + target_mmw $::_CHIPNAME.axi 0x44200520 0x200 0 +} + +lappend _telnet_autocomplete_skip _handshake_with_wrapper +# Uses AP0 +proc _handshake_with_wrapper { halt } { + set dbgmcu_cr 0 + catch {set dbgmcu_cr [eval $::_CHIPNAME.ap0 read_memory 0x80010004 32 1]} + if {[expr {($dbgmcu_cr & 0x07) == 0x00}]} { + echo "\nWARNING: FSBL wrapper not detected. Board in dev boot mode?\n" + return; + } + + if { $halt } { + if { $::EN_CA35_0 || $::EN_CA35_1 } { + $::_CHIPNAME.ap0 arp_examine + $::_CHIPNAME.ap0 arp_halt + } + if { $::EN_CA35_0 } { + $::_CHIPNAME.ap0 mww 0x80210300 0 + target_mmw $::_CHIPNAME.ap0 0x80210088 0x00004000 0 + } + if { $::EN_CA35_1 } { + $::_CHIPNAME.ap0 mww 0x80310300 0 + target_mmw $::_CHIPNAME.ap0 0x80310088 0x00004000 0 + } + if { $::EN_CM33 } { + $::_CHIPNAME.ap8 arp_examine + $::_CHIPNAME.ap8 arp_halt + $::_CHIPNAME.ap8 mww 0xe000edf0 0xa05f0001 + } + } + + # alert wrapper that debugger is ready + $::_CHIPNAME.ap0 mww 0x80010004 0x17 +} + +$_CHIPNAME.m33 configure -event reset-assert { } +$_CHIPNAME.m0p configure -event reset-assert { } + +$_CHIPNAME.axi configure -event reset-assert-post { adapter assert srst } + +$_CHIPNAME.axi configure -event reset-deassert-pre { + adapter deassert srst deassert trst + + $::_CHIPNAME.ap0 arp_examine + _handshake_with_wrapper $halt + + $::_CHIPNAME.axi arp_examine + _enable_debug + _rcc_enable_traceclk + if { $::EN_CA35_0 } { $::_CHIPNAME.a35_0 arp_examine; if {$halt} {$::_CHIPNAME.a35_0 arp_halt} } + if { $::EN_CA35_1 } { $::_CHIPNAME.a35_1 arp_examine; if {$halt} {$::_CHIPNAME.a35_1 arp_halt} } + if { $::EN_CM0P } { $::_CHIPNAME.ap2 arp_examine; $::_CHIPNAME.m0p arp_examine } + if { $::EN_CM33 } { + $::_CHIPNAME.ap8 arp_examine + $::_CHIPNAME.m33 arp_examine + if {$halt} {$::_CHIPNAME.m33 arp_halt} + } +} + +$_CHIPNAME.m0p configure -event examine-start { _enable_ap2_cm0p } + +$_CHIPNAME.axi configure -event examine-end { + _enable_debug + _rcc_enable_traceclk + if { $::EN_CA35_0 } { $::_CHIPNAME.a35_0 arp_examine } + if { $::EN_CA35_1 } { $::_CHIPNAME.a35_1 arp_examine } + if { $::EN_CM33 } { $::_CHIPNAME.ap8 arp_examine; $::_CHIPNAME.m33 arp_examine } + if { $::EN_CM0P } { $::_CHIPNAME.ap2 arp_examine; $::_CHIPNAME.m0p arp_examine } +} -- |

|

From: <ge...@op...> - 2025-07-03 05:11:27

|

This is an automated email from Gerrit. "Tomas Vanek <va...@fb...>" just uploaded a new patch set to Gerrit, which you can find at https://review.openocd.org/c/openocd/+/8981 -- gerrit commit 765e6e1a47c328f42856b1191c54482c204b00a7 Author: Tomas Vanek <va...@fb...> Date: Thu Jul 3 06:52:29 2025 +0200 flash/nor/stm32l4x: fix permanent write protection on STM32U5 Unlike other devices supported by this driver STM32U5 devices have a new UNLOCK bit in FLASH_WRP1AR, WRP1BR, WRP2AR, WRP2BR registers. Writing zero to this bit makes the write protection block permanent with no way to unprotect. Commit 6554d176e926 ("flash/stm32l4x: support STM32U59/U5Ax devices") and later commits with additional U5 devices lack support for the UNLOCK bit and therefore makes write protection permanent without warning. Introduce the new bit flag F_WRP_HAS_LOCK and mark U5 devices by it. Set UNLOCK bit in stm32l4_write_one_wrpxy() if F_WRP_HAS_LOCK is set. Change-Id: I26b97d855e094a21540e3377f367520683af2eac Signed-off-by: Tomas Vanek <va...@fb...> diff --git a/src/flash/nor/stm32l4x.c b/src/flash/nor/stm32l4x.c index f16333201b..8001aaf006 100644 --- a/src/flash/nor/stm32l4x.c +++ b/src/flash/nor/stm32l4x.c @@ -152,6 +152,9 @@ /* this flag indicates that programming should be done in quad-word * the default programming word size is double-word */ #define F_QUAD_WORD_PROG BIT(4) +/* the registers WRPxyR have UNLOCK bit - writing zero locks the write + * protection region permanently! */ +#define F_WRP_HAS_LOCK BIT(5) /* end of STM32L4 flags ******************************************************/ @@ -500,7 +503,8 @@ static const struct stm32l4_part_info stm32l4_parts[] = { .num_revs = ARRAY_SIZE(stm32u53_u54xx_revs), .device_str = "STM32U535/U545", .max_flash_size_kb = 512, - .flags = F_HAS_DUAL_BANK | F_QUAD_WORD_PROG | F_HAS_TZ | F_HAS_L5_FLASH_REGS, + .flags = F_HAS_DUAL_BANK | F_QUAD_WORD_PROG | F_HAS_TZ + | F_HAS_L5_FLASH_REGS | F_WRP_HAS_LOCK, .flash_regs_base = 0x40022000, .fsize_addr = 0x0BFA07A0, .otp_base = 0x0BFA0000, @@ -692,7 +696,8 @@ static const struct stm32l4_part_info stm32l4_parts[] = { .num_revs = ARRAY_SIZE(stm32u59_u5axx_revs), .device_str = "STM32U59/U5Axx", .max_flash_size_kb = 4096, - .flags = F_HAS_DUAL_BANK | F_QUAD_WORD_PROG | F_HAS_TZ | F_HAS_L5_FLASH_REGS, + .flags = F_HAS_DUAL_BANK | F_QUAD_WORD_PROG | F_HAS_TZ + | F_HAS_L5_FLASH_REGS | F_WRP_HAS_LOCK, .flash_regs_base = 0x40022000, .fsize_addr = 0x0BFA07A0, .otp_base = 0x0BFA0000, @@ -704,7 +709,8 @@ static const struct stm32l4_part_info stm32l4_parts[] = { .num_revs = ARRAY_SIZE(stm32u57_u58xx_revs), .device_str = "STM32U57/U58xx", .max_flash_size_kb = 2048, - .flags = F_HAS_DUAL_BANK | F_QUAD_WORD_PROG | F_HAS_TZ | F_HAS_L5_FLASH_REGS, + .flags = F_HAS_DUAL_BANK | F_QUAD_WORD_PROG | F_HAS_TZ + | F_HAS_L5_FLASH_REGS | F_WRP_HAS_LOCK, .flash_regs_base = 0x40022000, .fsize_addr = 0x0BFA07A0, .otp_base = 0x0BFA0000, @@ -716,7 +722,8 @@ static const struct stm32l4_part_info stm32l4_parts[] = { .num_revs = ARRAY_SIZE(stm32u5f_u5gxx_revs), .device_str = "STM32U5F/U5Gxx", .max_flash_size_kb = 4096, - .flags = F_HAS_DUAL_BANK | F_QUAD_WORD_PROG | F_HAS_TZ | F_HAS_L5_FLASH_REGS, + .flags = F_HAS_DUAL_BANK | F_QUAD_WORD_PROG | F_HAS_TZ + | F_HAS_L5_FLASH_REGS | F_WRP_HAS_LOCK, .flash_regs_base = 0x40022000, .fsize_addr = 0x0BFA07A0, .otp_base = 0x0BFA0000, @@ -1287,6 +1294,8 @@ static int stm32l4_write_one_wrpxy(struct flash_bank *bank, struct stm32l4_wrp * int wrp_end = wrpxy->last - wrpxy->offset; uint32_t wrp_value = (wrp_start & stm32l4_info->wrpxxr_mask) | ((wrp_end & stm32l4_info->wrpxxr_mask) << 16); + if (stm32l4_info->part_info->flags & F_WRP_HAS_LOCK) + wrp_value |= FLASH_WRPXYR_UNLOCK; return stm32l4_write_option(bank, stm32l4_info->flash_regs[wrpxy->reg_idx], wrp_value, 0xffffffff); } diff --git a/src/flash/nor/stm32l4x.h b/src/flash/nor/stm32l4x.h index 07b3615a24..1f4f2344f9 100644 --- a/src/flash/nor/stm32l4x.h +++ b/src/flash/nor/stm32l4x.h @@ -69,6 +69,9 @@ #define FLASH_U5_DUALBANK BIT(21) #define FLASH_TZEN BIT(31) +/* FLASH_WRPxyR register bits */ +#define FLASH_WRPXYR_UNLOCK BIT(31) + /* FLASH secure block based bank 1/2 register offsets */ #define FLASH_SECBB1(X) (0x80 + 4 * (X - 1)) #define FLASH_SECBB2(X) (0xA0 + 4 * (X - 1)) -- |

|

From: Stanislav S. <sta...@gm...> - 2025-07-03 00:44:25

|

Hello,

I'm debugging stm32mp157c MPU, the board named after QSMP comes from Ka-Ro

Electronics GmbH.

I'm running a debug session from lldb20 and there are a couple issues to

report.

1. When I try to check the sp_hyp register, lldb crashes. It seemed to me

that the problem is lldb itself until I tried to grab registers' descriptor

from openocd. It appears that something is wrong with numbering (see xlm in

the log below). I'm not 100% sure, that sequence must be continuous, I hope

someone can clarify it. If it must, the patch is one string to change

src/target/arm.h:ARM_VFP_V3_D0 value from 51 to 53. It works well, I also

checked that renumbering of d0-d31 registers does not affect values

displayed during the debug session.

2. The second issue is bound to lldp-dap (+ emacs + dap-mode in my setup),

which tries to dereference any 32 bit register which somehow reminds a

pointer... I have not investigated its heuristics but, for example, CPSR

register with its NZC flags in upper bits excites lldb-dap a lot. This

results in attempts to download a memory chunk from inaccessible memory

(given I have not initialized MMU), such as 0x60000000 or 0x80000000 - stm

does not map these regions. So it leads to stalling the session.

Nevertheless, if CPSR's upper flags bits show up as 0x400...., nothing bad

happens, as soon as 0x40000000 is a valid address for stm's periphery. I

have fixed it with a weird approach, given an alternative of pushing

patches into llvm seems undoable for me. CPSR's register could be marked 64

bit. This immediately cools down lldb's interest to dereference its value

at 32 bit armv7 arch and no attempts to access MPU memory are being

conducted.

Kind regards,

Stan

ws@ws:~ % lldb20 --version

lldb version 20.1.2

ws@ws:~ % lldb20

(lldb) file --arch armv7-none-none qsmp-fsbl

Current executable set to 'qsmp-fsbl' (armv7).

(lldb) gdb-remote 3333

(lldb) target modules load --load --set-pc-to-entry --slide 0

Process 1 stopped

* thread #1, stop reason = signal SIGINT

frame #0: 0x2ffc2500 qsmp-fsbl`fsbl._start [inlined] arch.goto at

arch.zig:329:5

326 }

327

328 pub inline fn goto(comptime func: anytype) void {

-> 329 asm volatile ("b %[addr]"

330 :

331 : [addr] "i" (func),

332 );

(lldb) process plugin packet send "qXfer:features:read:target.xml:0,10000"

packet: qXfer:features:read:target.xml:0,10000

response: l<?xml version="1.0"?>

<!DOCTYPE target SYSTEM "gdb-target.dtd">

<target version="1.0">

<architecture>arm</architecture>

<feature name="org.gnu.gdb.arm.core">

<reg name="r0" bitsize="32" regnum="0" save-restore="no" type="uint32"

group="general"/>

<reg name="r1" bitsize="32" regnum="1" save-restore="no" type="uint32"

group="general"/>

<reg name="r2" bitsize="32" regnum="2" save-restore="no" type="uint32"

group="general"/>

<reg name="r3" bitsize="32" regnum="3" save-restore="no" type="uint32"

group="general"/>

<reg name="r4" bitsize="32" regnum="4" save-restore="no" type="uint32"

group="general"/>

<reg name="r5" bitsize="32" regnum="5" save-restore="no" type="uint32"

group="general"/>

<reg name="r6" bitsize="32" regnum="6" save-restore="no" type="uint32"

group="general"/>

<reg name="r7" bitsize="32" regnum="7" save-restore="no" type="uint32"

group="general"/>

<reg name="r8" bitsize="32" regnum="8" save-restore="no" type="uint32"

group="general"/>

<reg name="r9" bitsize="32" regnum="9" save-restore="no" type="uint32"

group="general"/>

<reg name="r10" bitsize="32" regnum="10" save-restore="no" type="uint32"

group="general"/>

<reg name="r11" bitsize="32" regnum="11" save-restore="no" type="uint32"

group="general"/>

<reg name="r12" bitsize="32" regnum="12" save-restore="no" type="uint32"

group="general"/>

<reg name="sp" bitsize="32" regnum="13" save-restore="no" type="data_ptr"

group="general"/>

<reg name="lr" bitsize="32" regnum="14" save-restore="no" type="code_ptr"

group="general"/>

<reg name="pc" bitsize="32" regnum="15" save-restore="no" type="code_ptr"

group="general"/>

<reg name="cpsr" bitsize="32" regnum="25" save-restore="no" type="uint32"

group="general"/>

</feature>

<feature name="net.sourceforge.openocd.banked">

<reg name="sp_usr" bitsize="32" regnum="26" save-restore="no"

type="data_ptr" group="banked"/>

<reg name="lr_usr" bitsize="32" regnum="27" save-restore="no"

type="code_ptr" group="banked"/>

<reg name="r8_fiq" bitsize="32" regnum="28" save-restore="no" type="uint32"

group="banked"/>

<reg name="r9_fiq" bitsize="32" regnum="29" save-restore="no" type="uint32"

group="banked"/>

<reg name="r10_fiq" bitsize="32" regnum="30" save-restore="no"

type="uint32" group="banked"/>

<reg name="r11_fiq" bitsize="32" regnum="31" save-restore="no"

type="uint32" group="banked"/>

<reg name="r12_fiq" bitsize="32" regnum="32" save-restore="no"

type="uint32" group="banked"/>

<reg name="sp_fiq" bitsize="32" regnum="33" save-restore="no"

type="data_ptr" group="banked"/>

<reg name="lr_fiq" bitsize="32" regnum="34" save-restore="no"

type="code_ptr" group="banked"/>

<reg name="sp_irq" bitsize="32" regnum="35" save-restore="no"

type="data_ptr" group="banked"/>

<reg name="lr_irq" bitsize="32" regnum="36" save-restore="no"

type="code_ptr" group="banked"/>

<reg name="sp_svc" bitsize="32" regnum="37" save-restore="no"

type="data_ptr" group="banked"/>

<reg name="lr_svc" bitsize="32" regnum="38" save-restore="no"

type="code_ptr" group="banked"/>

<reg name="sp_abt" bitsize="32" regnum="39" save-restore="no"

type="data_ptr" group="banked"/>

<reg name="lr_abt" bitsize="32" regnum="40" save-restore="no"

type="code_ptr" group="banked"/>

<reg name="sp_und" bitsize="32" regnum="41" save-restore="no"

type="data_ptr" group="banked"/>

<reg name="lr_und" bitsize="32" regnum="42" save-restore="no"

type="code_ptr" group="banked"/>

<reg name="spsr_fiq" bitsize="32" regnum="43" save-restore="no"

type="uint32" group="banked"/>

<reg name="spsr_irq" bitsize="32" regnum="44" save-restore="no"

type="uint32" group="banked"/>

<reg name="spsr_svc" bitsize="32" regnum="45" save-restore="no"

type="uint32" group="banked"/>

<reg name="spsr_abt" bitsize="32" regnum="46" save-restore="no"

type="uint32" group="banked"/>

<reg name="spsr_und" bitsize="32" regnum="47" save-restore="no"

type="uint32" group="banked"/>

<reg name="sp_mon" bitsize="32" regnum="48" save-restore="no"

type="data_ptr" group="banked"/>

<reg name="lr_mon" bitsize="32" regnum="49" save-restore="no"

type="code_ptr" group="banked"/>

<reg name="spsr_mon" bitsize="32" regnum="50" save-restore="no"

type="uint32" group="banked"/>

<reg name="sp_hyp" bitsize="32" regnum="51" save-restore="no"

type="data_ptr" group="banked"/>

<reg name="spsr_hyp" bitsize="32" regnum="52" save-restore="no"

type="uint32" group="banked"/>

</feature>

<feature name="org.gnu.gdb.arm.vfp">

<reg name="d0" bitsize="64" regnum="51" save-restore="no"

type="ieee_double"/>

<reg name="d1" bitsize="64" regnum="52" save-restore="no"

type="ieee_double"/>

<reg name="d2" bitsize="64" regnum="53" save-restore="no"

type="ieee_double"/>

<reg name="d3" bitsize="64" regnum="54" save-restore="no"

type="ieee_double"/>

<reg name="d4" bitsize="64" regnum="55" save-restore="no"

type="ieee_double"/>

<reg name="d5" bitsize="64" regnum="56" save-restore="no"

type="ieee_double"/>

<reg name="d6" bitsize="64" regnum="57" save-restore="no"

type="ieee_double"/>

<reg name="d7" bitsize="64" regnum="58" save-restore="no"

type="ieee_double"/>

<reg name="d8" bitsize="64" regnum="59" save-restore="no"

type="ieee_double"/>

<reg name="d9" bitsize="64" regnum="60" save-restore="no"

type="ieee_double"/>

<reg name="d10" bitsize="64" regnum="61" save-restore="no"

type="ieee_double"/>

<reg name="d11" bitsize="64" regnum="62" save-restore="no"

type="ieee_double"/>

<reg name="d12" bitsize="64" regnum="63" save-restore="no"

type="ieee_double"/>

<reg name="d13" bitsize="64" regnum="64" save-restore="no"

type="ieee_double"/>

<reg name="d14" bitsize="64" regnum="65" save-restore="no"

type="ieee_double"/>

<reg name="d15" bitsize="64" regnum="66" save-restore="no"

type="ieee_double"/>

<reg name="d16" bitsize="64" regnum="67" save-restore="no"

type="ieee_double"/>

<reg name="d17" bitsize="64" regnum="68" save-restore="no"

type="ieee_double"/>

<reg name="d18" bitsize="64" regnum="69" save-restore="no"

type="ieee_double"/>

<reg name="d19" bitsize="64" regnum="70" save-restore="no"

type="ieee_double"/>

<reg name="d20" bitsize="64" regnum="71" save-restore="no"

type="ieee_double"/>

<reg name="d21" bitsize="64" regnum="72" save-restore="no"

type="ieee_double"/>

<reg name="d22" bitsize="64" regnum="73" save-restore="no"

type="ieee_double"/>

<reg name="d23" bitsize="64" regnum="74" save-restore="no"

type="ieee_double"/>

<reg name="d24" bitsize="64" regnum="75" save-restore="no"

type="ieee_double"/>

<reg name="d25" bitsize="64" regnum="76" save-restore="no"

type="ieee_double"/>

<reg name="d26" bitsize="64" regnum="77" save-restore="no"

type="ieee_double"/>

<reg name="d27" bitsize="64" regnum="78" save-restore="no"

type="ieee_double"/>

<reg name="d28" bitsize="64" regnum="79" save-restore="no"

type="ieee_double"/>

<reg name="d29" bitsize="64" regnum="80" save-restore="no"

type="ieee_double"/>

<reg name="d30" bitsize="64" regnum="81" save-restore="no"

type="ieee_double"/>

<reg name="d31" bitsize="64" regnum="82" save-restore="no"

type="ieee_double"/>

<reg name="fpscr" bitsize="32" regnum="83" save-restore="no" type="int"

group="float"/>

</feature>

</target>

(lldb) register read sp_hyp

PLEASE submit a bug report to https://github.com/llvm/llvm-project/issues/

and include the crash backtrace.

Stack dump:

0. Program arguments: /usr/local/llvm20/bin/lldb

1. HandleCommand(command = "register read sp_hyp")

#0 0x00000008304040a9 llvm::sys::PrintStackTrace(llvm::raw_ostream&, int)

(/usr/local/llvm20/lib/libLLVM.so.20.1+0x44040a9)

#1 0x0000000830401f55 llvm::sys::RunSignalHandlers()

(/usr/local/llvm20/lib/libLLVM.so.20.1+0x4401f55)

#2 0x00000008304047b7 (/usr/local/llvm20/lib/libLLVM.so.20.1+0x44047b7)

#3 0x00000008218064a0 (/lib/libthr.so.3+0x1a4a0)

#4 0x0000000821805a6b (/lib/libthr.so.3+0x19a6b)

#5 0x00000008214702d3 ([vdso]+0x2d3)

#6 0x00000008256c12dc memcpy (/lib/libc.so.7+0x15a2dc)

#7 0x0000000824625991 (/usr/local/llvm20/lib/liblldb.so.20.1+0xe25991)

#8 0x000000082462553c (/usr/local/llvm20/lib/liblldb.so.20.1+0xe2553c)

#9 0x0000000824624f8d (/usr/local/llvm20/lib/liblldb.so.20.1+0xe24f8d)

#10 0x00000008247dac30 (/usr/local/llvm20/lib/liblldb.so.20.1+0xfdac30)

#11 0x00000008247da4ee (/usr/local/llvm20/lib/liblldb.so.20.1+0xfda4ee)

#12 0x0000000824234b31 (/usr/local/llvm20/lib/liblldb.so.20.1+0xa34b31)

#13 0x000000082422524b (/usr/local/llvm20/lib/liblldb.so.20.1+0xa2524b)

#14 0x000000082422993e (/usr/local/llvm20/lib/liblldb.so.20.1+0xa2993e)

#15 0x000000082418c5f0 (/usr/local/llvm20/lib/liblldb.so.20.1+0x98c5f0)

#16 0x000000082416b9e2 (/usr/local/llvm20/lib/liblldb.so.20.1+0x96b9e2)

#17 0x000000082422b8ad (/usr/local/llvm20/lib/liblldb.so.20.1+0xa2b8ad)

#18 0x0000000823e1e0eb lldb::SBDebugger::RunCommandInterpreter(bool, bool)

(/usr/local/llvm20/lib/liblldb.so.20.1+0x61e0eb)

#19 0x000000000020a873 (/usr/local/llvm20/bin/lldb+0x20a873)

#20 0x000000000020b3b9 (/usr/local/llvm20/bin/lldb+0x20b3b9)

#21 0x00000008255ece34 __libc_start1 (/lib/libc.so.7+0x85e34)

LLDB diagnostics will be written to /tmp/diagnostics-19f8fe

Please include the directory content when filing a bug report

Segmentation fault (core dumped)

|

|

From: Den <de...@us...> - 2025-07-02 13:05:49

|

thank you for the information! so it's not because of the fronts that it doesn't work. so the problem is something else. --- **[tickets:#456] aducm360 swd could not find MEM-AP** **Status:** new **Milestone:** 0.10.0 **Labels:** aducm360_swd **Created:** Tue Jul 01, 2025 01:58 PM UTC by Den **Last Updated:** Wed Jul 02, 2025 12:19 PM UTC **Owner:** nobody **Attachments:** - [attach.zip](https://sourceforge.net/p/openocd/tickets/456/attachment/attach.zip) (751.5 kB; application/x-zip-compressed) aducm360 not connect to openocd via jtag-swd. adapter based on ftdi2232 used original config aducm360.cfg used my config ftdi_swd.cfg tested in openocd v10 & v12 command: openocd.exe -d0 -f \interface\ftdi\ftdi_swd.cfg -f target\aducm360.cfg -c init -c targets -c "reset halt" -c "flash erase 0" -c shutdown log: debug_level: 0 cortex_m reset_config vectreset Error: [aducm360.cpu] Could not find MEM-AP to control the core TargetName Type Endian TapName State -- ------------------ ---------- ------ ------------------ ------------ 0* aducm360.cpu cortex_m little aducm360.cpu unknown Error: [aducm360.cpu] Could not find MEM-AP to control the core Error: [aducm360.cpu] Debug AP not available, reset NOT asserted! in attach log from debug level 3 ftdi_swd.cfg log saleae logic 1.2.18 --- Sent from sourceforge.net because ope...@li... is subscribed to https://sourceforge.net/p/openocd/tickets/ To unsubscribe from further messages, a project admin can change settings at https://sourceforge.net/p/openocd/admin/tickets/options. Or, if this is a mailing list, you can unsubscribe from the mailing list. |

|

From: Tomas V. <to...@us...> - 2025-07-02 12:19:08

|

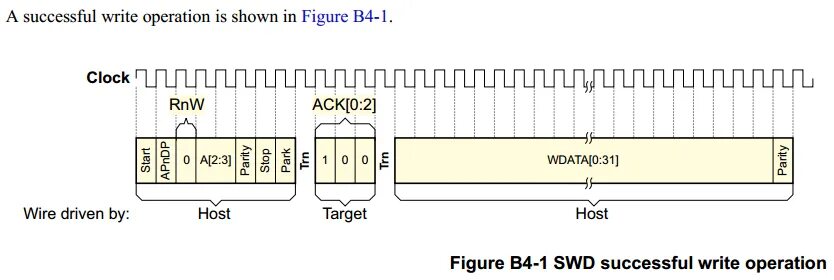

Don't be fooled by this simplified diagram found in ARM documentation: it's so simplified that it's wrong. SWDIO correctly changes on failing SWCLK edge when the adapter transmits and on rising SWCLK edge when SWDP transmits. See 8690: target/arm_adi: add URLs of latest ARM ADI spec | https://review.openocd.org/c/openocd/+/8690 https://documentation-service.arm.com/static/5ea6eaba9931941038df04ff?token= --- **[tickets:#456] aducm360 swd could not find MEM-AP** **Status:** new **Milestone:** 0.10.0 **Labels:** aducm360_swd **Created:** Tue Jul 01, 2025 01:58 PM UTC by Den **Last Updated:** Wed Jul 02, 2025 11:48 AM UTC **Owner:** nobody **Attachments:** - [attach.zip](https://sourceforge.net/p/openocd/tickets/456/attachment/attach.zip) (751.5 kB; application/x-zip-compressed) aducm360 not connect to openocd via jtag-swd. adapter based on ftdi2232 used original config aducm360.cfg used my config ftdi_swd.cfg tested in openocd v10 & v12 command: openocd.exe -d0 -f \interface\ftdi\ftdi_swd.cfg -f target\aducm360.cfg -c init -c targets -c "reset halt" -c "flash erase 0" -c shutdown log: debug_level: 0 cortex_m reset_config vectreset Error: [aducm360.cpu] Could not find MEM-AP to control the core TargetName Type Endian TapName State -- ------------------ ---------- ------ ------------------ ------------ 0* aducm360.cpu cortex_m little aducm360.cpu unknown Error: [aducm360.cpu] Could not find MEM-AP to control the core Error: [aducm360.cpu] Debug AP not available, reset NOT asserted! in attach log from debug level 3 ftdi_swd.cfg log saleae logic 1.2.18 --- Sent from sourceforge.net because ope...@li... is subscribed to https://sourceforge.net/p/openocd/tickets/ To unsubscribe from further messages, a project admin can change settings at https://sourceforge.net/p/openocd/admin/tickets/options. Or, if this is a mailing list, you can unsubscribe from the mailing list. |

|

From: Den <de...@us...> - 2025-07-02 11:48:25

|

Judging by the cyclogram from the analyzer, it is possible that the adapter does not correctly set the SWDIO bits in relation to the SWCLK clock signal. When transmitting from the adapter, the SWDIO bits are set when the SCLK clock signal drops from 1 to 0 (falling edge), although on the found protocol waveforms, the SWDIO data should be set when the difference is from 0 to 1 (rising edge), and read along the falling edge. At the same time, the device sets the bits on the correct SWCLK edge. Can someone fix it?  --- **[tickets:#456] aducm360 swd could not find MEM-AP** **Status:** new **Milestone:** 0.10.0 **Labels:** aducm360_swd **Created:** Tue Jul 01, 2025 01:58 PM UTC by Den **Last Updated:** Tue Jul 01, 2025 01:58 PM UTC **Owner:** nobody **Attachments:** - [attach.zip](https://sourceforge.net/p/openocd/tickets/456/attachment/attach.zip) (751.5 kB; application/x-zip-compressed) aducm360 not connect to openocd via jtag-swd. adapter based on ftdi2232 used original config aducm360.cfg used my config ftdi_swd.cfg tested in openocd v10 & v12 command: openocd.exe -d0 -f \interface\ftdi\ftdi_swd.cfg -f target\aducm360.cfg -c init -c targets -c "reset halt" -c "flash erase 0" -c shutdown log: debug_level: 0 cortex_m reset_config vectreset Error: [aducm360.cpu] Could not find MEM-AP to control the core TargetName Type Endian TapName State -- ------------------ ---------- ------ ------------------ ------------ 0* aducm360.cpu cortex_m little aducm360.cpu unknown Error: [aducm360.cpu] Could not find MEM-AP to control the core Error: [aducm360.cpu] Debug AP not available, reset NOT asserted! in attach log from debug level 3 ftdi_swd.cfg log saleae logic 1.2.18 --- Sent from sourceforge.net because ope...@li... is subscribed to https://sourceforge.net/p/openocd/tickets/ To unsubscribe from further messages, a project admin can change settings at https://sourceforge.net/p/openocd/admin/tickets/options. Or, if this is a mailing list, you can unsubscribe from the mailing list. |

|

From: Den <de...@us...> - 2025-07-01 13:58:40

|